本资源包括了ZYNQ-7000系列SOC,管脚分配信息以及BANK分区信息,对ZYNQ硬件电路设计很有帮助

”ZYNQ-7000 FPGA 管脚分配表“ 的搜索结果

对于Zynq-7000系列的所有型号,其PFGA管脚分配表都涵盖了大量的信息。这些型号包括但不限于Z-7010、Z-7015、Z-7020、Z-7030、Z-7035和Z-7045。以下是一些可能列出的管脚分配信息: - 信号名称和描述:每个管脚都有...

注:本文为笔者自己翻译的XILINX ZYNQ-7000 SOC UG-585官方文档,文档版本UG585 (v1.12.2) July 1, 2018 文章目录第2章 信号、接口和引脚2.1 介绍2.2 电源引脚2.3 PS I/O引脚2.4 PS-PL电平转换器使能2.5 PS-PL MIO-...

Zynq-7000 SoC处理系统PS的构成应用处理器单元 (APU) 应用处理单元高性能特性,兼容ARM处理器 即:存储器单元DDR控制器Quad-SPI控制器静态存储器控制器I/O外设两个三模式以太网控制器两个USB控制器两个SD\SDIO控制器两...

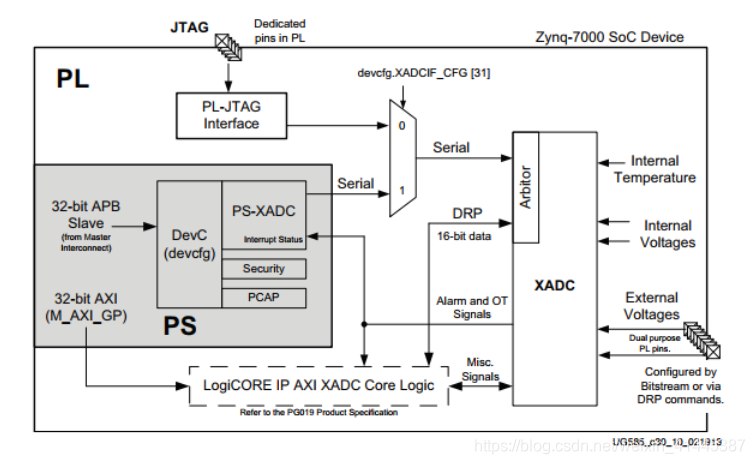

Zynq-7000 PS重配置PL

标签: 嵌入式

Zynq-7000的结构分为PS(ARM)和PL(FPGA),当然也可以理解为PL作为一种外设挂载在PS端。在正常的系统加载顺序(FALSH \ SD -> FSBL -> PL ->BITSTRAM ->PS ELF)完成后重新配置PL程序,可以利用XLINX官方...

包含ZYNQ7000系列中的AX7010、AX7020芯片原理图结构图等硬件资料:AX7020开发板原理图V2.0、AX7020开发板PCB设计图、AX7020尺寸结构、AX7010_AX7020管脚。

一、整体概述此板卡是由南京米联电子设计团队设计的一款高性能SOC开发板。采用了美国XILINX公司开发的XC7Z020CLG484作为CPU,硬件设计方案参考了安富利公司的Zedboard,最大程度实现了软件和硬件的兼。...

multi-region Clock引脚,具有时钟功能的引脚,当时钟是单端时,时钟信号必须由MRCC引脚的正端输入。1.8V,PS的PLL供电电压,在它附近必须放置0.47uf—4.7uf的电容。

xilinx zynq-7000 基本知识 2015-09-01 19:12 4313人阅读 评论(1) 收藏 举报 分类: 读书笔记(4) 版权声明:本文为博主原创文章,未经博主允许不得转载。 Zynq-7000 采用可...

ZYNQ7000引脚-个人理解

标签: fpga

② ug865-Zynq-7000-Pkg-Pinout.pdf 一、引脚描述 本文以xc7z020clg400为例,进行说明。所有400个引脚如下图所示。 User I/O Pins 其中, Configuration Pins Power/Ground Pins PS MIO Pins PS DDR Pins ...

0.引言 构建SoC系统,毕竟是需要实现PS和PL间的数据交互,而像上一讲那样PL主机与PL从机之间通过AXI4-Lite总线进行交互有点杀鸡用牛刀了。 如果PS与PL端进行数据交互,可以直接设计PL端为从机,PS端向PL端的reg...

XILINX官网连接:https://www.xilinx.com/support/package-pinout-files.html

一、整体概述 4 二、应用领域及人群 4 三、硬件配置 4 BANK资源分配 6 四、MiZ701开发板功能描述 7 4.1 全编程SOC(All Programmable SoC) 7 4.2 内存(Memory) 7 4.2.1 DDR3 7 4.2.2 PROM SPI FALSH 8 4.2.3 TF ...

1.ZYNQ 7000 PS端和PL端都有自己独立的电源引脚(Power Pin) 2.PS端接口和信号: PS_CLK(System reference clock) POR_RST_N(Power on reset, active low.) SRST_N(Debug system reset) DDR Memory接口 ...

Xilinx 公司的 FPGA 芯片主要分为两大类,FPGA 和 SoC(System on Chip,片上处理系统),其中 FPGA 芯片只包含了可编程逻辑部分,而不包含处理器,如常见的 Spartan 系列、Artix 系列、Kintex 系列和 Virtex 系列。...

简述DDS与FIR原理,并在Vivado工具链下用FPGA实现两者,适合初学者进行学习和练习

PYNQ-Z2是一款基于Xilinx Zynq-7000系列SoC的开发板,其中集成了FPGA和双核ARM Cortex-A9处理器,具有丰富的I/O接口和资源。该开发板可用于各种应用场景,如嵌入式系统设计、数字信号处理、机器学习等。 对于基于...

在ZYNQ-7000平台上利用PS点亮PL上的LED灯 1、实验方案 图1 实验方案系统框图 2、具体步骤 2.1、vivado工程建立 ①打开vivado集成开发环境,点击“Create Project”,如下图所示。 ②点击“Next”,如下...

嵌入式开发之zynqMp —Zynq UltraScale+ MPSoC 图像编码板zcu102 转载地址:https://www.cnblogs.com/pengkunfan/p/8569986.html 1.1 xilinx zynqMp 架构 1.1.1 16nm 级别工艺 Zynq UltraScale+ ...

学习内容 使用SDK和提供的API进行初始化GPIO,并驱动led和btn进行操作,实现led呼吸灯效果,串口读取btn的值。 开发环境 vivado 18.3 && SDK 开发板 pynq-z2 ...我们可以简单的理解为zynq这个芯片是

推荐文章

- withRouter,非根组件获取路由参数_withrouter 只能取到路由中的一个参数-程序员宅基地

- ubuntu环境下QT5操作摄像头报错,cannot find -lpulse-mainloop-glib cannot find -lpulse cannot find -lglib-2.0_cannot find–lpulse-程序员宅基地

- 用jbpm_bpel学jwsdp的ant方式使用-程序员宅基地

- 输入数字判断星期几_html获取当前星期几-程序员宅基地

- SpringBoot整合Activiti7——实战之放假流程(会签)_activit7中会签-程序员宅基地

- 阿里云服务器收到挖矿病毒的攻击,导致基础的文件被病毒污染的问题和对应的处理解决方法-程序员宅基地

- 北京东城区空调维修办法,格力变频空调出现ph,到底是怎么回事?_格力变频空调ph代码-程序员宅基地

- vscode编辑器使用拓展插件background添加背景图片改变外观_background vscode-程序员宅基地

- android 简单打电话程序_android拨打电话的程序-程序员宅基地

- 第二届中国(泰州)国际装备高层次人才创新创业大赛_泰州市双创人才计划2022-程序员宅基地